SiC MOSFET 在 6.6kW 高频率高功率密度功率转换器中的应用

Article

摘要

本文介绍了碳化硅 (SiC) 器件在高频率 LLC 谐振 DC/DC 转换器中的应用。此类转换器可用于母线转换器、电动汽车充电机、服务器电源和储能系统。在开关频率较高的情况下,LLC 变压器的漏电感可用作谐振电感,在 500kHz 和 6.6kW/400V 输出下,可以使得体积和重量减少 50%,磁性元件的功率损耗减少 30%。实验结果表明,在输出为 400V/16A 的变频器中,SiC 功率器件的性能优于 Si 基功率器件,在 500kHz 时的转换器峰值效率接近 98.5%。

1 简介

高效率和高功率密度一直是开关电源的持续需求[1]。随着碳化硅 (SiC) 器件等宽禁带 (WBG) 功率器件的技术开发和应用,使其在许多应用领域有望成为传统硅 (Si) 器件的替代品。由于它们具有出色的开关速度和较低的开关损耗,以及导通电阻 (RDS_ON) 的低温依赖性,因此可以实现更高的效率、更高的功率密度、以及更高的鲁棒性和可靠性 [2-5]。此项研究将展示在 500kHz 到 1.5MHz 下,SiC MOSFET 在 6.6kW DC/DC 转换器中的性能。高频率操作的主要优点是变压器和 EMI 滤波器更小,而且变压器中集成了谐振电感,这进一步减小了转换器的尺寸。与传统的 100kHz - 200kHz DC/DC 转换器相比,在 500kHz 下运行的电路磁性元件的体积和重量减少了 50%,LLC 转换器(400V/16A 输出)的峰值效率接近 98.5%。由于 ZVS 产生的串扰要小得多,因此 SiC MOSFET 即使在没有负偏置驱动电压的情况下也可以可靠运行,从而降低了驱动电路成本。本文将介绍高频操作的实用设计指南,如 PCB 布局、磁芯材料和气隙选择、绕组线尺寸和结构、谐振电容器的选择等,并给出试验结果。

2 高频率 LLC DC/DC 转换器的模拟

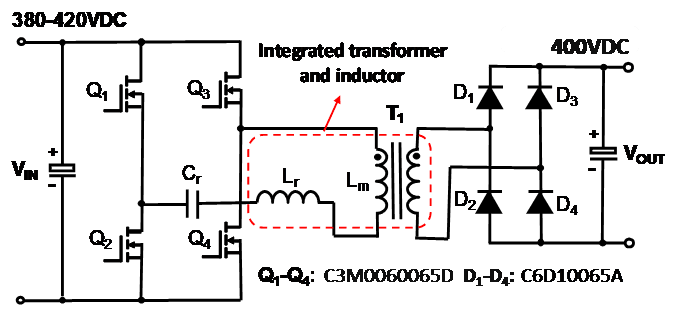

利用 LTspice 对 SiC MOSFET 的性能以及影响转换器效率的因素进行模拟研究。图 1 显示的是一个全桥 LLC DC/DC 转换器的简化原理图。当开关频率为 500kHz,磁化电感 Lm = 30 mH 时,四个初级开关的模拟总功耗为 80.24W(每个 20.06W),由于所有主开关的 ZVS 导通,二极管作为输出整流器,总效率达到 98.11%。

较大的磁化电感 Lm 可以减小磁化电流,降低初级开关的导通损耗;但 Lm 的取值也需要提供足够的磁化电流来使漏极-源极电容完全放电,并确保在死区期间初级开关 ZVS 的导通。因此,Lm 应满足 (1) [6]。

其中,td 是上、下开关两个栅极驱动信号之间的死区时间,fs 是开关频率,CTotal 是总电容,包括初级开关的漏极-源极电容、PCB 的寄生电容和次级侧二极管的反射电容。对于给定的死区时间 td,可以根据 (1) 对 Lm 进行优化设计,实现正常工作时的高效率。

3 设计注意事项

3.1 LLC 变压器的设计

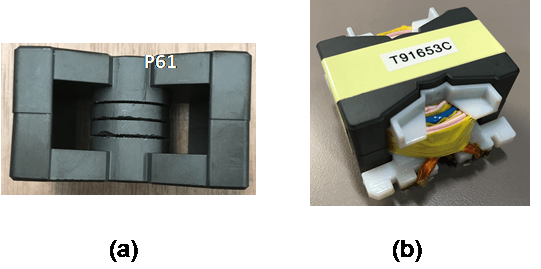

用 (1) 计算出最大磁化电感后,进行高频率操作时,需要仔细考虑磁芯材料、气隙和导线尺寸,否则会造成极大的功率损耗,导致变压器因过热而发生意外故障。在适用于高频率的磁芯材料中,选择了 Acme 的 P61,因为它的功率损耗低,而且易于获得用于大功率应用的磁芯形状,开关频率范围从 500kHz 到 1MHz。初步测试使用了 PQ50/28 磁芯。一次绕组 (f0.05mm´360´4) 和二次绕组 (f0.05mm´400´2 TIW) 都使用 Litz 导线,每个绕组有 9 圈。为了减少由气隙附近的边缘磁通引起的铜损,使用了三个分布式气隙而不是一个大的气隙,如图 2 所示。

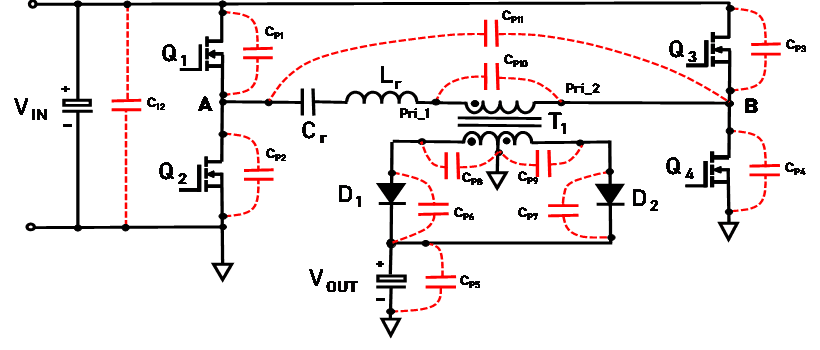

3.2 PCB 布局

PCB 布局对 EMI、信号完整性以及电路效率和操作起着至关重要的作用,尤其是对于高频率 LLC 转换器而言。图 3 显示了 LLC 转换器实验 PCB 中存在的寄生电容(版本 1 和版本 2)。版本 1 的 PCB 采用了较大面积的铜片,目的是为了减少 PCB 线路的功率损耗和消除电流回路的磁场;但是,由于不同铜层之间存在较大面积的重叠,因此产生了表 I 所示的较大寄生电容。版本 2 的 PCB 的铜线和迹线重叠区域小得多,因此其产生的寄生电容大大降低。使用手持 LRC 测量仪在裸露的 PCB(没有填充任何部件)上测量寄生电容。在 LLC 电路中,开关 (CP1-CP4)、变压器绕组 (CP8-CP10) 和初级侧中点 (CP11) 之间的大寄生电容会导致不希望出现的效率下降(如表 I 所示,测得效率下降了 0.8%,功率损耗增加了 26W)。因此,需要在降低铜损和寄生效应之间进行权衡。

PCB Version | CP1 | CP2 | CP3 | CP4 | CP5 | CP6 | CP7 | CP8 | CP9 | CP10 | CP11 | CP12 | Efficiency (%) | Power Loss (W) |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

Ver. 1 | 315 | 390 | 343 | 420 | 4860 | 534 | 620 | 535 | 598 | 508 | 896 | 1385 | 95.71 | 141.57 |

Ver. 2 | 17 | 22 | 25 | 28 | 4731 | 528 | 516 | 589 | 575 | 11 | 13 | 308 | 96.50 | 115.50 |

4 实验结果

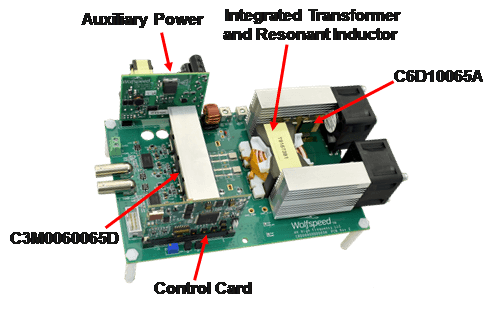

图 4 显示的是功率密度为 128 W/in3 的原型图,初级开关采用 TO-247-3 封装的 SiC MOSFET (C3M0060065D, 60 mW/650 V),输出整流器采用 TO-220 封装的 SiC 二极管 (C6D10065A, 10 A/650 V)。由于高频率操作,谐振电感采用了主变压器的漏电感 (1mH),因而不需要外部电感。基于 TI DSP 的控制卡 (TMDSCNCD280049C) 用于产生开环操作或闭环操作所需的栅极驱动信号,以调节输出电压。辅助电源(WolfSpeed 提供的 CRD-15DD17P)为控制电路和栅极驱动器供电。

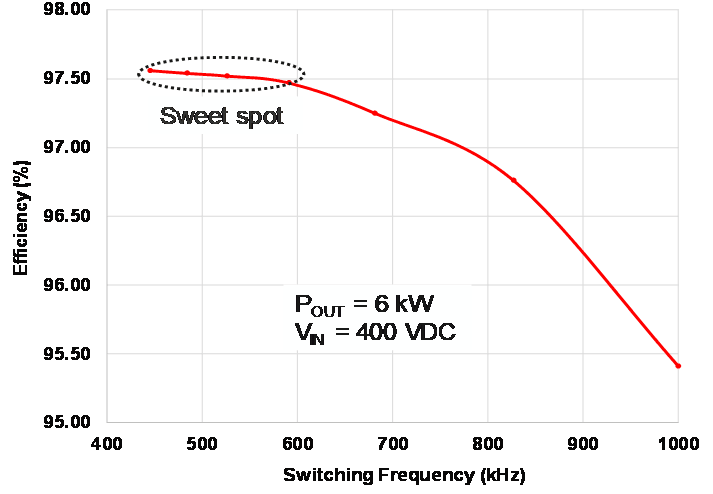

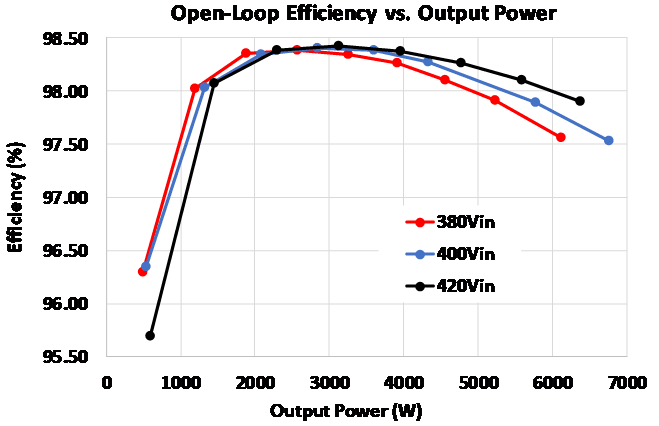

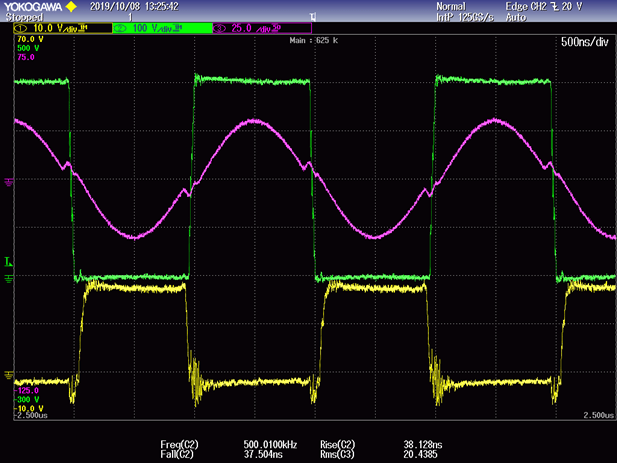

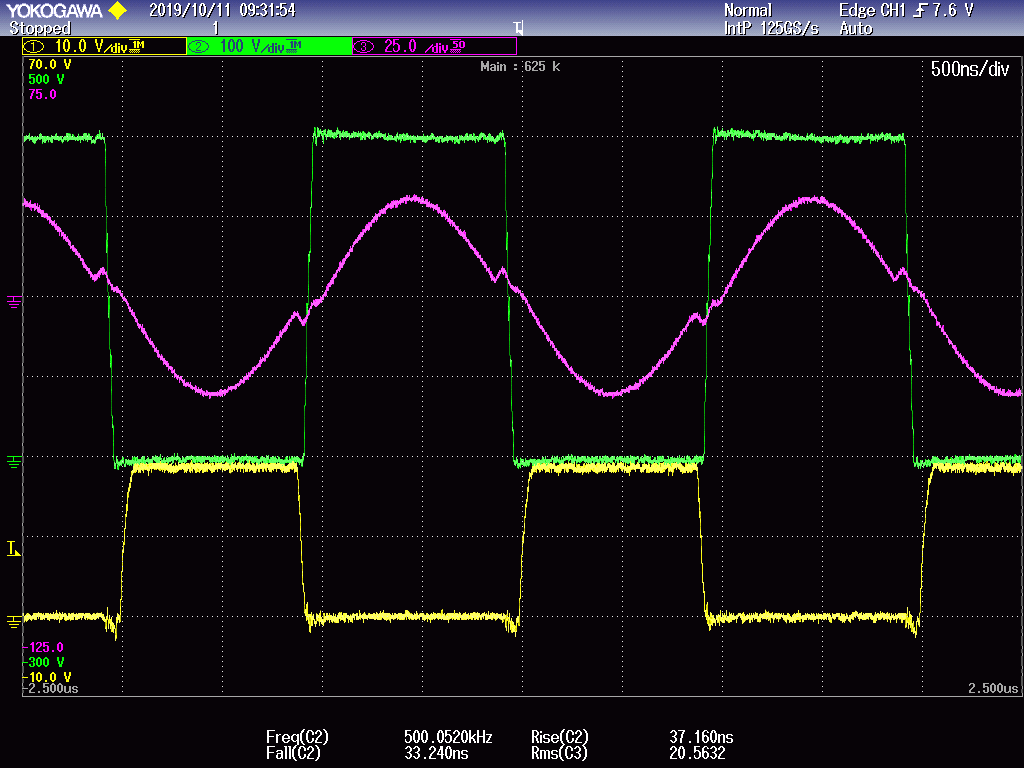

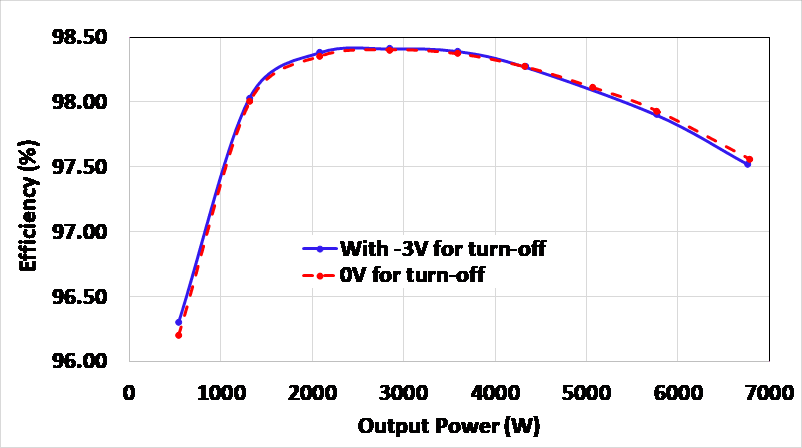

图 5 显示了在 400V/16A 直流输出下,测量效率与开关频率的关系。最佳开关频率范围为 500kHz 到 650kHz,效率无明显下降。随着开关频率的增加,效率的下降主要是由于 LLC 变压器 [7]-[9] 中与频率相关的铜损和磁芯损耗增加,以及 PCB 线路损耗。频率从 500kHz 增加到 1MHz 时,栅极驱动导致的功耗增加了 2.2W,而每个 MOSFET 的功耗增加了 3.5W(模拟时从 20.06W 增加到 23.56W)。图 6 显示了开环操作中效率与输出功率的关系图。在半负载(约 3kW)时,可实现约 98.5% 的峰值效率。图 7 显示了初级侧上开关捕获的栅极-源极和漏极-源极波形,以及在 550kHz 和 400V 输入时初级侧谐振电流波形。

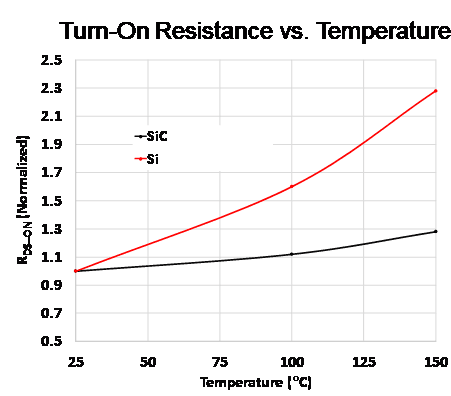

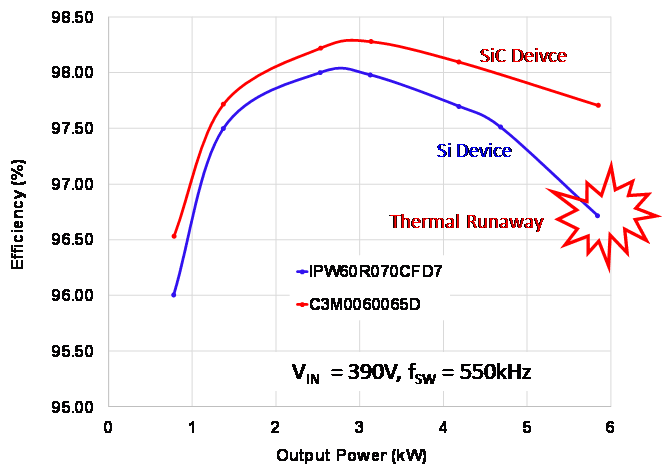

此外,我们还与初级侧�开关的 Si 基功率器件(英飞凌的 IPW60R70CFD7,57mW/600V)进行了对比测试。与 Si 基 MOSFET 相比,SiC 基 Wolfspeed 器件 C3M0060065D 的导通电阻随结温升高而增加的幅度要小得多。图 8 显示了这两种器件的导通电阻与温度的关系图。在 150°C 时,SiC 器件的归一化导通电阻为 1.3,而 Si 基器件则达到 2.3。图 9 显示了不同功率器件的效率与输出功率的关系图。Si 基 MOSFET 由于其导通电阻随温度的升高而显著增加,开关损耗较大,在高功率时效率降低 1%,在相同的散热条件下已进入热失控状态。

对于在半桥或全桥电路中使用的 MOSFET 的关断,通常建议使用负栅极驱动电压(对于 C3M006065D 为-3V~-4V),以防止因高 dv/dt 引起的串扰而导致快速开关器件的误导通。但是,在 LLC 电路中,所有开关都是在零电压下通过软开关导通的,所以 dv/dt 要低得多,不会发生严重的串扰。因此,可以不需要开关关断的负电压,以降低驱动电路的复杂度和成本。图 10 显示了在没有栅极驱动负电压情况下捕获的波形。从图 11 中未观察到异常栅极驱动信号,也未看到明显的效率差异。

5 结论

本文介绍了一种采用 SiC MOSFET 和集成磁性元件的 LLC 谐振 DC/DC 转换器,并在 500kHz - 1.5MHz 范围内进行了全面测试。研究发现,精心设计的 PCB 布局和变压器是实现高转换效率的关键。在功率密度为 128W/in3 的情况下,获得了超过 98% 的峰值效率。测试效率数据和捕获的波形表明,SiC MOSFET 在比传统 Si 基器件高得多的频率下操作时具有优越的性能。此外,测试表明,在谐振 LLC 拓扑中,由于 ZVS 引起的串扰较小,即使在没有用于关断功率器件的负驱动电压的情况下,SiC MOSFET 也能够可靠地操作,因此降低了驱动的复杂度和成本。这些宽禁带器件在各种应用中为高效率、高功率密度的功率转换提供了前所未有的机会。未来的研究将把平面磁性元件与表面贴装功率器件结合起来,以实现更高功率密度转换器的设计。

参考文献

- M. Paolucci, “Improving Power Density and Efficiency in Servers and Telecom,” Power Systems Design, Nov. 2015.

- R. Wang, P. Ning, Z. Wang, et al., “A High-Temperature SiC Three Phase AC-DC Converter Design for > 100 °C Ambient Temperature,” IEEE Trans. Power Electronics, vol. 28, no. 1, pp 55-572, Jan. 2013.

- L. Zhang, S. Guo, X. Li, et al., "Integrated SiC MOSFET Module with Ultralow Parasitic Inductance for Noise Free Ultrahigh Speed Switching," in Wide Bandgap Power Devices and Applications (WiPDA), 2015 IEEE 3rd Workshop, pp.224-229, 2-4 Nov. 2015.

- J. W. Palmour, L. Cheng, V. Pala, et al., “Silicon Carbide Power MOSFETs: Breakthrough Performance from 900 V up to 15 kV,” in Power Semiconductor, pp.79–82, 15–19 June 2014.

- G. Wang, F. Wang, G. Magai, et al., “Performance Comparison of 1200V 100A SiC MOSFET and 1200V 100A Silicon IGBT,” in 2013 IEEE ECCE, pp.3230-3234, 15–19 Sept. 2013.

- B. Lu, W. Liu, Y. Liang, et al., “Optimal Design Methodology for LLC Resonant Converter,” IEEE-APEC Proc., 2006, pp. 533-538.

- W. G. Hurley, E. Gath, and J. G. Breslin, “Optimizing the AC Resistance of Multilayer Transformer Windings with Arbitrary Current Waveforms,” IEEE Transactions on Power Electronics, pp. 369-376, Vol. 15, No. 2, March 2000. 369–76.

- C. R. Sullivan, “Optimal Choice for Number of Strands in a Litz-Wire Transformer Winding,” IEEE Transactions on Power Electronics, pp.283-291, Vol. 14, No. 2, March 19.