功率模組:符合EMI的捷徑

Article

相鄰或共用導電回路的電子元件容易受到電磁干擾 (EMI) 的影響,使其工作過程受到干擾。要確保各電氣系統在同一環境中不干擾彼此的正常運行,就必須最大限度地減少發射。通常,由於矽 (Si) IGBT 和碳化矽 (SiC) MOSFET 等功率半導體元件在工作期間需要進行快速切換,因此通常會產生傳導型 EMI。在切換狀態轉換過程中,元件兩端的電壓和流經元件的電流會迅速改變狀態。切換狀態間變化會產生 dv/dt 和 di/dt,從而在切換頻率的諧波頻率上產生 EMI。

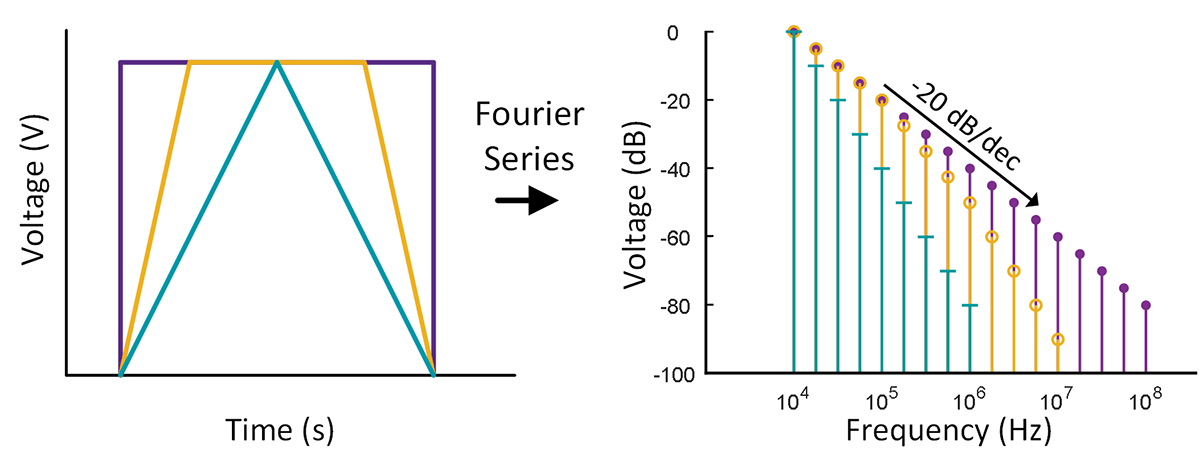

切換頻率和邊延速率(即元件的狀態改變速度)決定了在切換期間產生的 EMI。通常情況下,最高發射值會出現在切換頻率,較��低峰值則出現在切換頻率的整數倍。例如,如果切換頻率為 100 kHz,那麼將在 100 kHz、200 kHz、300 kHz 等頻率出現發射頻譜尖峰。圖 1 展示了具有不同上升時間的脈衝波形在不同頻率條件下的頻譜發射衰減情況。對於具有無限 dv/dt 和 di/dt 值的理想方形波,發射頻譜的幅度將以 20 dB/十倍頻程的速度遞減。對於具有最慢 dv/dt 和 di/dt 的理想三角形波,頻譜將下降 40 dB/十倍頻程。因此,對於電力電子設備所產生的梯形波,頻譜衰減將在 20 dB/十倍頻程到 40 dB/十倍頻程之間,衰減幅度取決於邊延速率。隨著元件切換速度加快,諧波頻率的發射頻譜預計會增加,而跨頻衰減速度將減慢。

這就需要電力電子設計師在切換頻率、邊延速率和所產生的 EMI 之間進行一系列權衡。為了提高密度,設計師可能會選擇提高切換頻率。這將減少低次諧波,但由於頻譜包絡移動到較高頻而可能導致輻射增加。此外,切換頻率升高會增加切換損耗。為了彌補總體損耗的增加,設計師可能會選擇提高邊延速率(di/dt 和 dv/dt),以減少切換損耗。但是,邊緣速度越快,會反過來增加系統在較高頻率時的發射。因此,隨著在應用場景中提高切換頻率和採用高效能、寬頻隙元件(如 SiC),設計師必須考慮 EMI 的影響。

抑制方式

系統的整體發射不僅取決於電力電子設備的開關切換,還取決於所產生的雜訊與其他系統的耦合方式。我們的目標是將控制系統內切換元件所產生的頻譜內容,或將發射移離關鍵元件。為此,常用方法是在電力電子設備的輸入和輸出端增加 EMI 濾波器,這些濾波器允許所需頻率自由通過,同時重新定向或吸收掉不需要的頻率。然而,EMI 濾波器體積大且價格昂貴,因此必須縮小其尺寸以優化成本和功率密度。一種更有效的方法是在設計初期就考慮耦合問題。通過策略性地優化系統內的小的寄生耦合參數,或通過在系統內的寄生耦合周圍平衡佈置無源元件,可在不使用 EMI 濾波器的情況下大�幅減少發射。這樣,設計師就能通過另一種方法來優化系統並最大限度地減少發射,同時還能利用碳化矽在提升效率和功率密度方面的優勢。不過,這種方法要求設計師對元件和系統有著深入的瞭解,但並不總是能直觀獲取。

散熱器耦合的影響

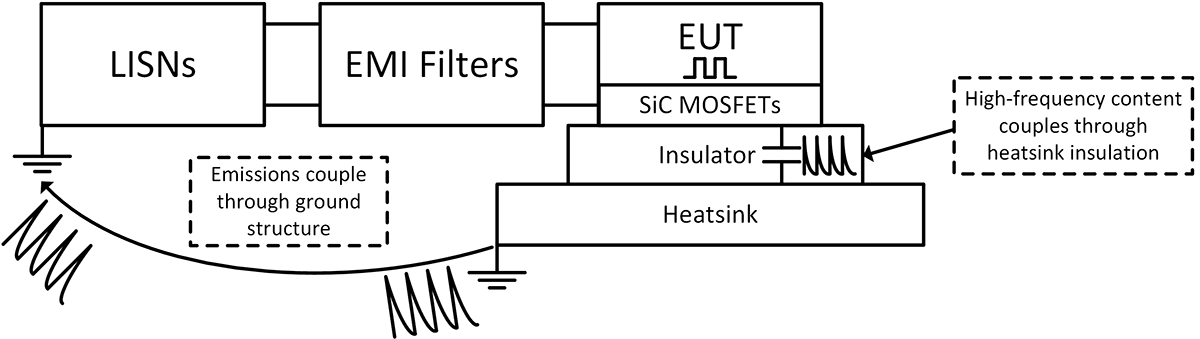

寄生電容是電力電子系統中普遍採用的一種重要寄生耦合,位於半導體和散熱器之間。一般而言,會在半導體和散熱器之間放置一個絕緣的導熱材料。然而,這實際上是在絕緣體上形成一個小平行板電容,高頻共模電流可在此流動,從而提供了向系統發射的額外路徑。圖 2 舉例說明了這一概念。被測設備 (EUT) 是指完整的變換器或逆變器系統,而線路阻抗穩定網路 (LISN) 是用於EMC規範測試的元件,為系統提供已知的輸入阻抗。在運行過程中,EUT 產生的高頻共模雜訊會通過半導體的絕緣電容流向底板,然後流向散熱器,再流向 LISN 等其他系統元件。

這可能會使頻譜光譜升高,從而導致 EUT 無法通過發射規範測試。這種情況與許多實際系統相符,在這些系統中,通常出於安全性和易實施性因素而將散熱器接地。因此,在設計應用時必須考慮這一 CM 雜訊路徑,以滿足規範要求。

功率模組的優勢

功率模組在電氣與散熱方面的特色比分離式元件擁有更大的優勢,提供更高的功率密度,在某些情況下還可以簡化組裝過程。優勢之一,是使用陶瓷絕緣體將半導體元件的高電壓導體與模組的金屬底板區隔開來。因此模組可以直接附加到接地的散熱器或是其他散熱管理系統上,無需使用其他絕緣材料。此外,由於陶瓷特性與厚度受到嚴格控管,功率模組會讓每個樣本都維持一致的電容。因此,模組設計的電容耦合可以量化,並獨立於實作電容耦合的系統之外。這個情況與經常使用絕緣矽墊的分離式元件不同:

- 可能在各個樣本或安裝扭矩之間產生不同的電容耦合

- 取決於系統的幾何尺寸而不是半導體元件,使得它必須等待整個系統完成才能量化

功率模組具有恆定一致的耦合值,因此在功率轉換器的設計階段才能夠模擬,並減少 EMI。對於功率模組而言,半導體和底板之間的絕緣電容稱為底板電容 (BPC)。

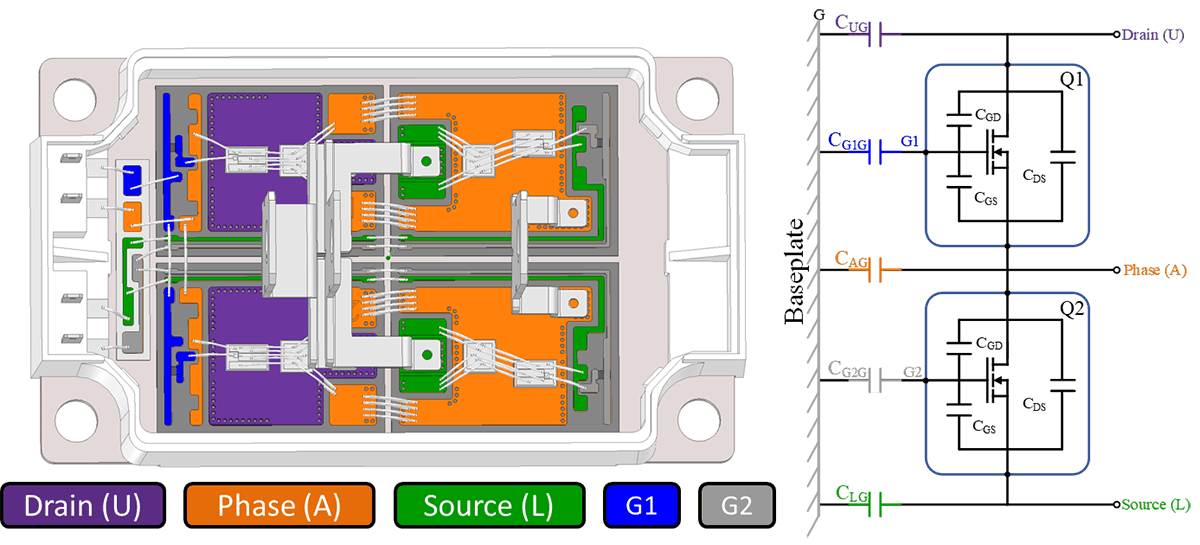

電容分佈

瞭解寄生底板電容分佈對 EMI 的影響也很重要。除各底板電容的總和值外,這些電容之間的比率也對整體共模發射有著決定性影響。在某些情況下,甚至可以將這些電容調整為特定的比率,從而在不使用濾波器的情況下大幅降低共模電流。圖 3 舉例說明了 Wolfspeed CAS175M12BM3 模組中底板電容的分佈情況。通過直連的各底板區域顯示為一種顏色,並應將其作為單個集中電容進行建模。由於開爾文源極走線連接到晶片頂部的相應源極引腳,因此它們與源極節點集中在一起。一般而言,底板區域的面積越大,電容耦合越高。對於半橋模組,完整 BPC 模型包括五個底板電容:每個功率端子各有一個,以及每個閘極各一個。各底板電容的這一邏輯也適用於任何模組拓撲結構。

EMI 模擬

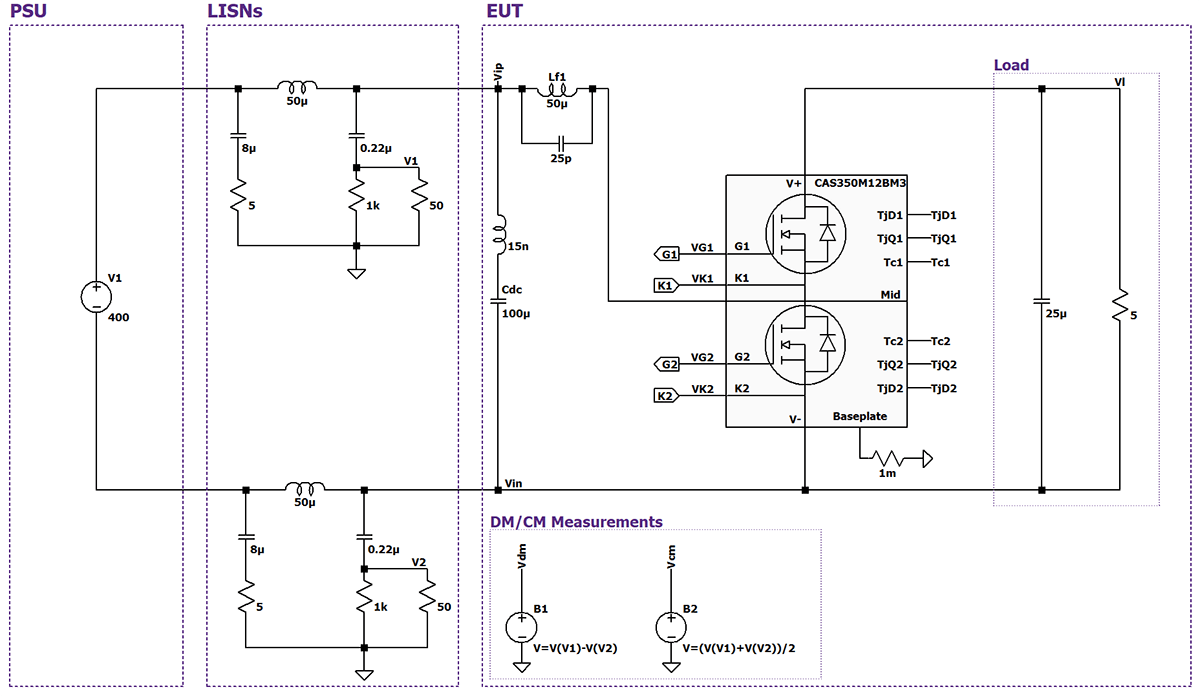

電路級模擬軟體(如 LTspice)對於研究寄生與其他參數對 EMI 的影響有極大幫助。Wolfspeed 的功率模組 SPICE 模型已針對在速度和精度方面進行了優化,並在封裝模型中包含寄生底板電容,因此可有效地用於執行 EMI 模擬。請注意,由於系統和周圍環境之間的小的寄生耦合比較複雜,因此很難正確預測物理系統的發射。不過,設計師可通過模擬來研究寄生元件對發射的影響,或者試驗各種濾波器設計。為證明底板電容對 EMI 的影響,在封裝模型有和無底板電容的情況下評估了圖 4 中的 EMC 升壓轉換器模擬。

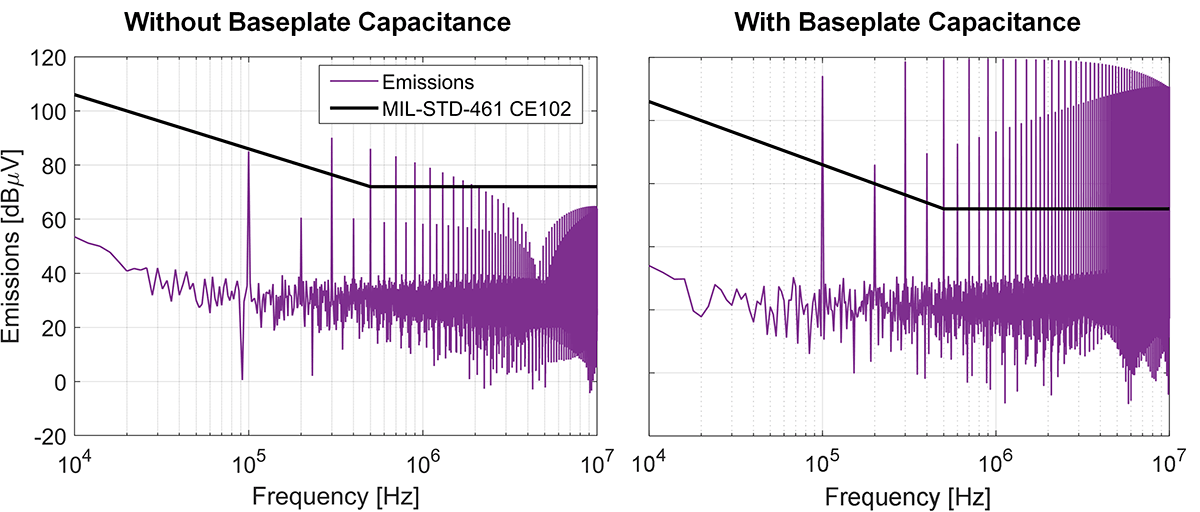

有底板電容和無底板電容時 V1 的光譜波形如圖 5 所示。圖中疊加了 MIL-STD-461 CE102 的發射限制條件;高於此線的任何光譜含量都表示未滿足該標準。雖然在這兩種配置條件下系統都不符合 EMC 要求(考慮到未使用 EMI 濾波器,這並不奇怪),但有底板電容的系統在 100 kHz 至 10 MHz 範圍內的光譜含量高於發射線限制。而無底板電容的系統在 2 MHz 以上頻率時符合標準。請注意,這只是一個理想化示例;在實際系統中,還會有其他共模路徑與底板電容並聯。

從這角度,設計師可以利用模擬來應用濾波器、評估寄生耦合的影響、研究共模抑制技術,並進一步瞭解其系統然後再投入時間和資金進行實證EMC規範測試。不過,只有在功率模組的底板電容已知並納入模擬中的情況下,模擬才有效。Wolfspeed 已對其所有功率模組平台進行測量,並發佈了相關數據資料。