柵極驅動器以及SiC MOSFET的柵極驅動

Article

碳化矽(SiC)MOSFET的使用促使了多個應用的高效率電力輸送,比如電動車快速充電、電源、可再生能源以及電網基礎設施。雖然它們的表現比傳統的矽(Si)MOSFET和 IGBT 更為出色,但驅動方式卻不盡相同,必須要在設計過程中進行縝密的思考。以下是一些SiC柵極驅動器的一些示例要求:

- 驅動供電電壓包含開通的正壓和關斷的負壓

- 共模瞬態抗擾度(CMTI)大於100 kV/µs

- 最大工作絕緣電壓可達1700 V

- 驅動能力可達10 A

- 傳輸延遲時間和頻道不匹配時間小於 10 ns

- 主動米勒鉗位

- 快速短路保護(SCP)(小於1.8 µs)

對於 SiC MOSFET的一般驅動考慮

鑒於這些要求,需要考慮幾個隔離柵極驅動器技術。磁耦合驅動器是一個相對成熟的技術,但是在磁場應用中也會成為一個令人關切的問題。電容耦合驅動器具備來自高電壓應力和改進後對外部磁場抗擾度的出色保護,同時以最低的延遲提供非常迅捷的開關。但是,這項技術仍然容易受高電場應用問題的影響。作為更為傳統的絕緣方式、光耦合非常有效並可提供出色的瞬變和噪音保護,但是由於曝光增加和LED特性,隨著時間推進會逐漸減弱。

隨著系統功率和頻率增加,柵極驅動功率要求也會提高。設計人員應確保驅動器具備足夠的驅動能力保證MOSFET完全導通。保持柵極驅動器內部FET RDS(on)處於低位以及更高的電流傳輸和更快的開關速度,但是總驅動平均功率要求取決於開關頻率、總柵極電荷(以及任何其置於柵極上的電容)、柵極電壓擺動以及並聯 SiC MOSFET的數量或P=(Freq x Qg x Vgs(total)x N)。其中P是平均功率,Freq是開關頻率,Qg是總柵極電荷,Vgs(total)是總柵極電壓擺動,N是並聯數量。

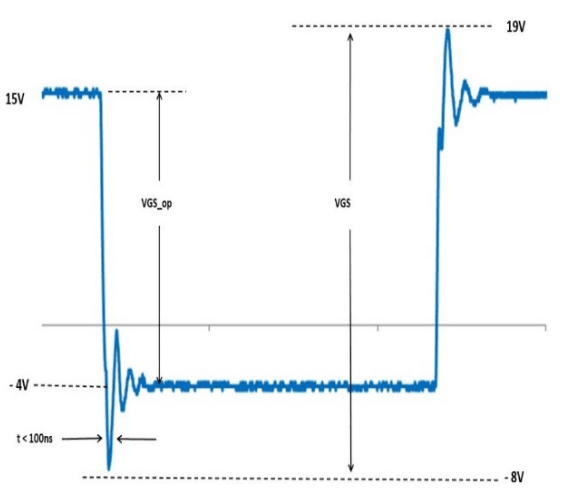

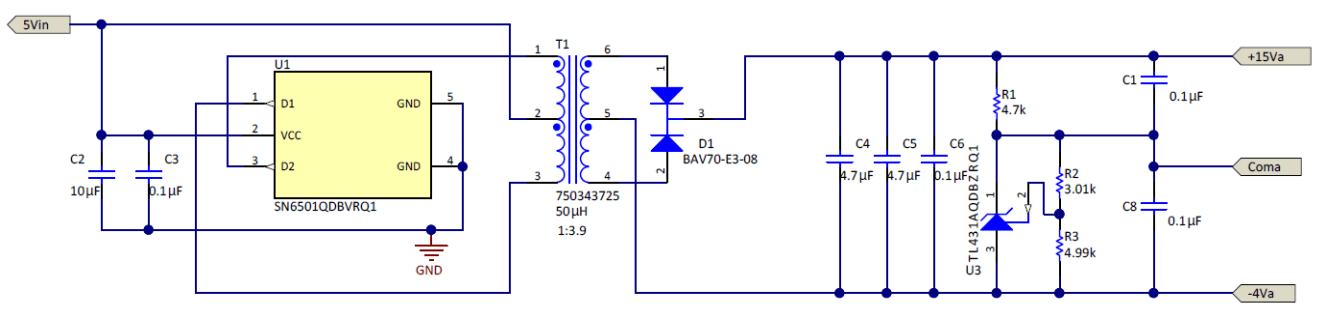

開關時往往存在振盪和過沖,正如圖 1 當中所示的那樣,所以需要特別關注器件的最大VGS 額定值。對於開通/關斷時的驅動電源電壓選擇,推薦(15 V, - 4 V)以確保安全運行和長期可靠性。驅動電壓可以接受 ± 5% 的公差。對於帶有相對緊湊回饋控制的或帶有線性穩壓的輔助電源,± 5% 甚至 ± 2% 的公差是可以實現的。

SiC MOSFET比 Si MOSFET 開關速度更快��,所以 SiC 柵極驅動器的設計要求能夠承受更高dV/dt(開關期間漏極-源極電壓變化率)是非常關鍵的,因為這會對MOSFET造成振盪和損壞。在硬開關應用中,SiC MOSFET能夠產生超過150 V/ns的dV/dt,所以推薦使用帶有高CMTI 額定值的驅動器。

一些PCB佈局建議及技巧

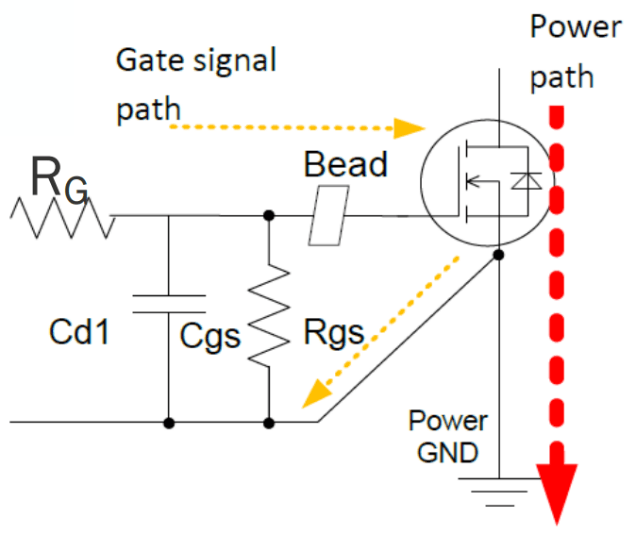

對稱的PCB佈局對於並聯應用時降低驅動環路內的環流而言非常關鍵。另外,保證驅動回路和功率回路分開可防止串擾,而增加抑制效應(如柵極電阻器和鐵氧體磁珠)可以減小柵極振盪。置於MOSFET柵極和源極之間的小型電容(100 pF到1 nF)可為高頻雜訊電流提供低阻抗路徑(見圖 2)。

以下是需要考慮的一些佈局相關的事項:

- 保證柵極驅動回路和功率環路分開,儘量不要有任何交疊。

- 由於 SiC 系統中的高di/dt和dV/dt,寄生電感和電容能夠對性能和開關行為產生巨大影響。對降低寄生效應的一些建議:

- 當選用外掛程式封裝 MOSFET 時儘量使用最短的引腳長度;

- 減小驅動晶片到 MOSFET 的距離;

- 在母線和功率地之間放置低阻抗的薄膜電容或者瓷片電容;

- 對於直流匯流排,使用較大的鋪銅面積;

- 避免開關節點和母線以及其他敏感信號的交疊;

- 讓高頻率磁性材料遠離敏感信號;

- 開關節點上的電容會增加損耗。

- 匯流排環路中的電感增加關閉時的電壓過沖。

- 柵極回路中的電感和電容降低開關速度和驅動電壓的控制。

- 並聯應用電感或電容的不同會導致不平衡。

並聯MOSFET可提升應用的功率

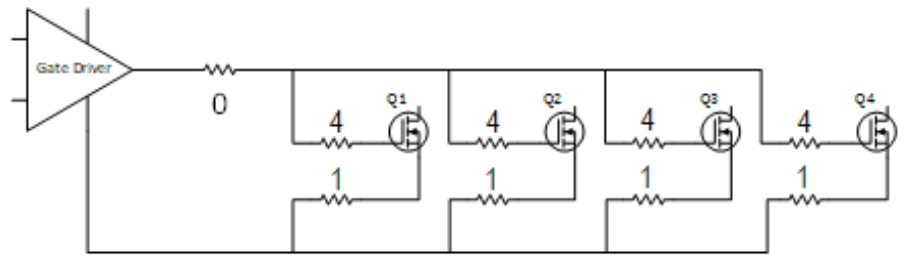

並聯MOSFET促使大功率設計成為現實(比如交錯並聯升壓轉換器)。當用一個驅動器驅動並聯MOSFET時,它們的柵極不應直接連在一起,而是將外置的驅動電阻單獨應用到每個SIC MOSFET的柵極。雜散電感(範圍介於1到15 nH之間)也可產生不平衡的震盪電壓,但是增加柵極電阻和增加鐵氧體磁珠可以增加抑制效應以説明降低震盪和開關損耗。並且在每個 SiC MOSFET的驅動回路的Kelvin source添加一個1 Ω 電阻器可以大幅降低任何可能流動的高峰值電流,以及作為到VGS的自動回饋(見圖 3)。

當使用模組時,一些相同規則仍舊適用。當對模組進行並聯時,設計人員可在分享的柵極驅動器和單獨的柵極驅動器之間進行選擇。分享柵極驅動器有助於消除不同驅動器之間的不匹配問題,但是很難對柵極驅動器進行對稱佈局,特別是對超過兩個並聯模組而言。

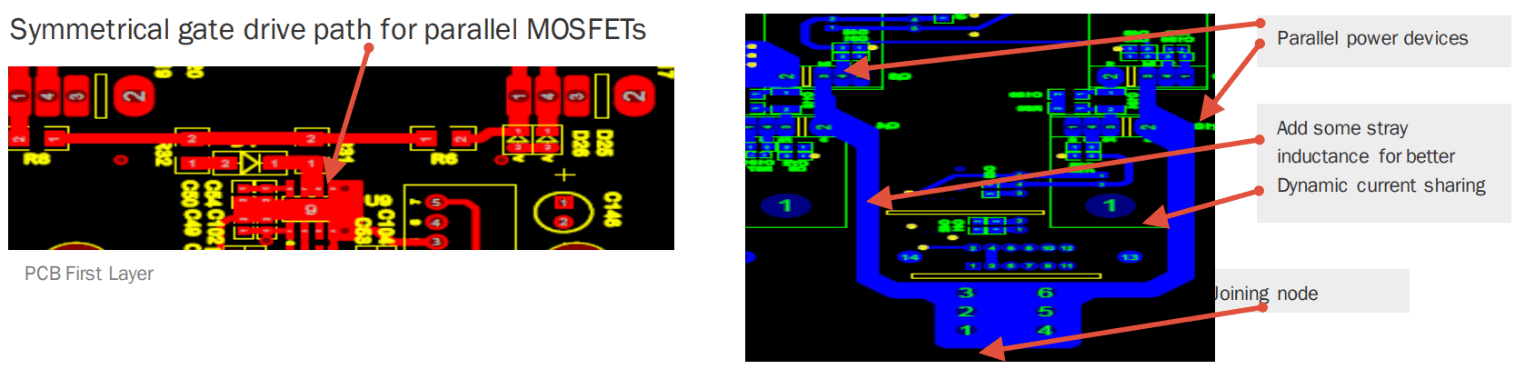

圖 4顯示的是佈局並聯MOSFET驅動器板的一些佈局示例。

負驅動電壓保證更安全的運行並改善抗干擾度

通常情況下,MOSFET在0 V時完全關閉。增加負柵極偏壓會改善抗干擾度並避免在橋式電路應用中出現誤開通,但是對於單端型功率轉換器,比如反激式、升壓或降壓轉換器,可以接受使用0-V關斷電壓。當使用圖騰柱拓撲時,高dV/dt和di/dt通常會導致串擾並能在柵極生成振盪的電壓尖峰,因此負電壓關斷(比如 - 4 V)能防止誤開通,同時保證最大允許負壓 - 8 V有足夠的餘量。如果 PCB 佈局已得到優化,只要沒有誤開通,負柵極偏壓可以接近 - 3 V 或 - 2 V(依次降低該偏壓可以降低體二極體的正向電壓)。

正負柵極驅動電壓解決方案可通過多種方式完成。例如,專用 15 V / - 3 V 集成電源元件可以説明降低部件數量,而在一個穩定的18 V輸出後加上電阻器和齊納二極體生成 - 3 V 可以提供更多的靈活性。另一個方案是使用帶有內置DC/DC控制器的柵極驅動器IC,比如Si8281。最後,通過使用推挽電路,比如來自德州儀器的TIDA-01605,你可以定制你自己的完整解決方案(見圖 5)。

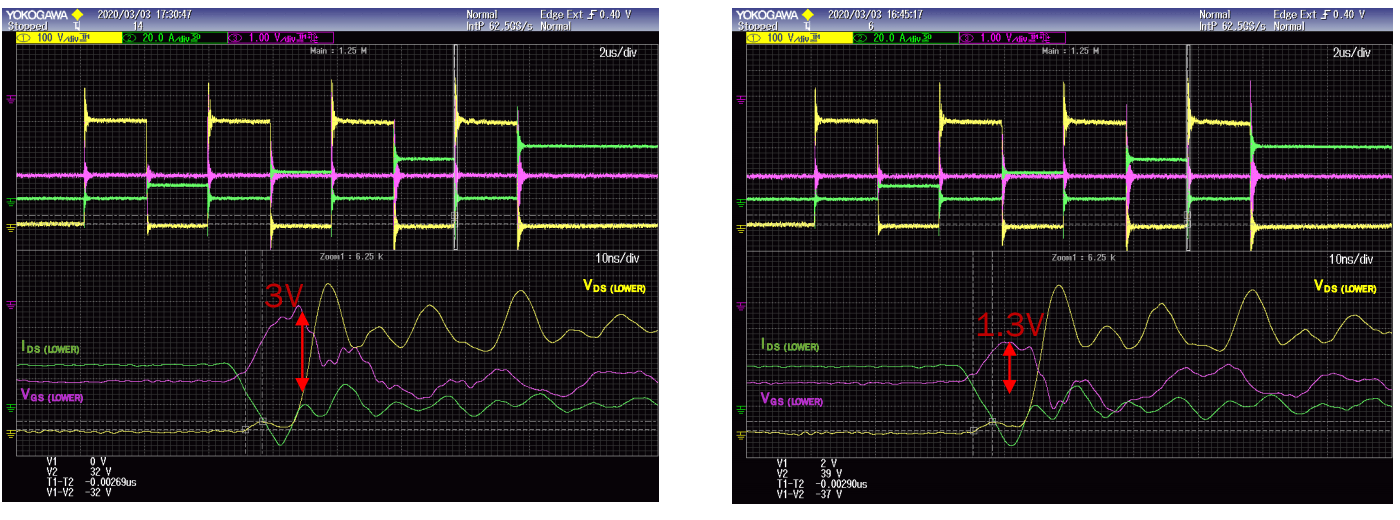

當 MOSFET 關斷時,在圖騰柱半橋設計中增加主動米勒鉗位可以大幅降低串擾(對於在400 VDC下使用C3M0060065J的對比,見 圖 6)。為實現更好的鉗位效果,驅動器須儘量接近MOSFET,這樣雜散電感就會達到最小化。

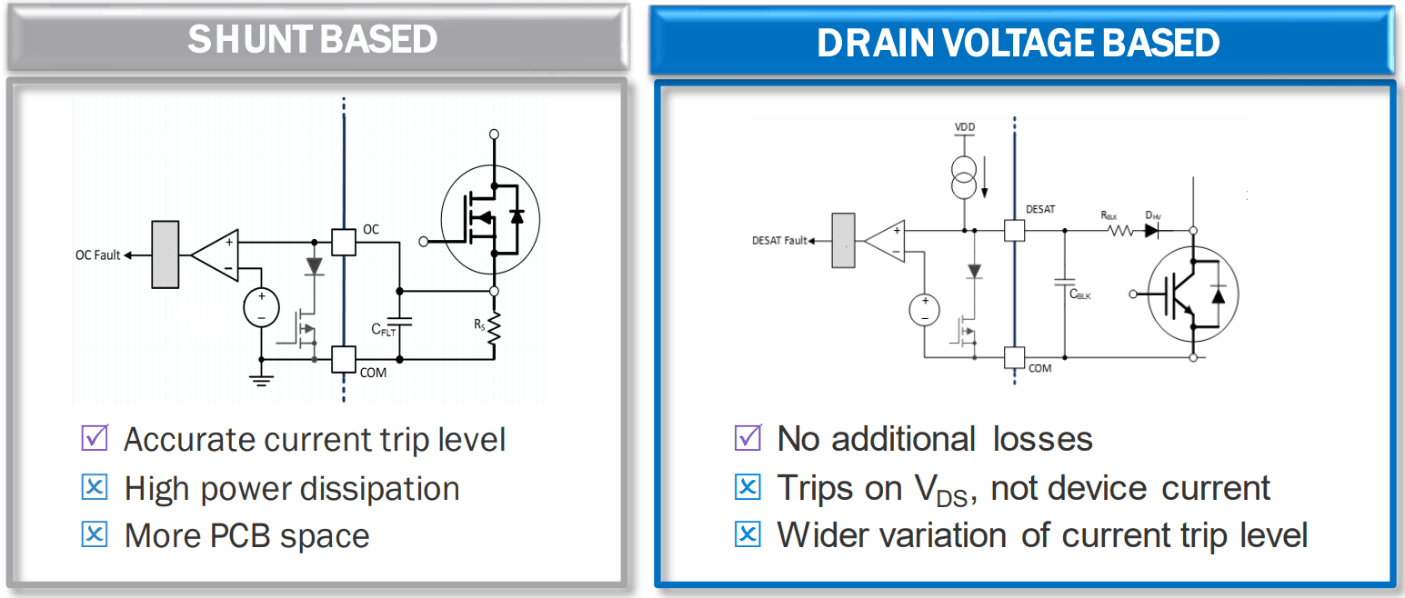

其他推薦的測試和微調

保護你的設計免受超載電流(或短路)的影響是一個必須要考慮的問題,相較於電流分流器,大部分設計人員還是傾向于採用“退飽和”方式。雖然電流分流器能提供更精確的斷路電平,但它消耗了很多電力,同時需要大量的PCB空間。因此電流分流器更多用於需要準確的電流保護點的低功率應用。對於 SiC 來說,去飽和機制表現出色,因為它沒有引入額外的損耗並能夠用於大功率載荷/模組。圖 7顯示了用於 SiC MOSFET的基於分流器和基於漏極電壓短路保護設計之間的差異。

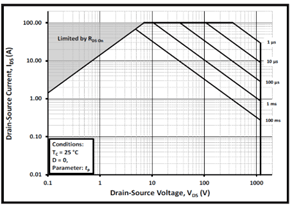

短路保護的設計非常重要,但是微調切斷參數卻非常棘手。設計人員須充分保護 SiC MOSFET,同時不允許任何誤動作。“去飽和”電壓水準須基於MOSFET的RDS(on),連同最壞情況下的條件,包括高溫、峰值電流和RDS(on)最大值進行選擇。應基於開關過渡時間和抗干擾度來選擇去飽和檢測時間,同時須考慮最壞情況下的條件,比如低電流以及大電流波動。為確保 SiC 裸片無有害效應,Wolfspeed推薦以下保守建議: 打開後檢測時間為250 - 500 ns,在檢測後軟停機持續時間為400 - 1,500 ns,短路持續時間不超過1 - 1.5 µs。

在大部分 SiC 模組中,當器件仍處於波動(小於1 ms)且未飽和時,須檢測短路故障。不同於IGBT,SiC 器件的故障可能必須在短路電流到達峰值之前才能檢測到。可進行破壞測試來檢驗這個特性,比如圖 8中所示的測試示例。這項測試包含ADuM4177柵極驅動器和CAB450M12XM3 SiC 模組(額定值為1,200 V / 450 A)。故障應在550 ns內得到檢測並在之後360 ns內停機。

總結

綜上所述,SiC 技術使高效率和高功率密度系統成為現實,但須考慮多個策略進行驅動。柵極驅動器須具備足夠的驅動能力來降低損耗,且在足夠高的開關頻率下運行時,它必須具備高 CMTI、最低的寄生電感以及優化的去飽和檢測和軟停機特性x。當佈局 PCB 時,減小驅動回路寄生電感以防止串擾,同時使用被動元件,如電容和鐵氧體磁珠也可有效抑制干擾。同時對於並聯應用時,單獨的柵極電阻及對稱的 PCB 佈局能保證均流。