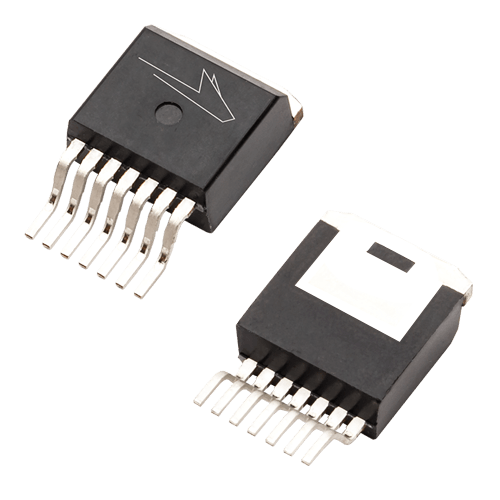

The purpose of this evaluation board is to demonstrate the proper design and layout for paralleling two high performance Wolfspeed

® Silicon Carbide (SiC) MOSFETs in a 7-pin D2PAK™ package. This evaluation board comes configured as a half bridge but it can be configured into other common topologies such as a synchronous boost or synchronous buck topology. This board was designed to make it easy for the user to:

- Evaluate dynamic and steady-state current sharing of parallel SiC MOSFETs

- Evaluate SiC MOSFET switching performance and characterize EON and EOFF losses in SiC MOSFETs.

- Evaluate SiC MOSFET thermal performance in a synchronous buck or boost converter.

- Use as a PCB layout example for effectively paralleling SiC MOSFETs.

- Use as a reference for thermal management of a D2PAK SiC MOSFET

Wolfspeed and Keysight Technologies, Inc. have worked together to develop a PathWave Advanced Design System (ADS) workspace for this evaluation board that allows designers to simulate the design including parasitic effects of the PCB layout. This workspace demonstrates how to use the ADS platform to optimize a PCB layout for paralleling Silicon Carbide MOSFETs faster and at lower cost than a conventional prototype-test design cycle. For details on the ADS workspace and to request a trial license,

click here.