A Designer’s Guide to Silicon Carbide: Quality, Qualification, and Long-Term Reliability

Article

Over the past decade, the incorporation of Silicon Carbide (SiC) in power, LED, and RF devices has steadily increased, allowing for this technology to progressively mature in all aspects. This is due to the many desirable qualities this wide-bandgap substrate has relative to its silicon (Si)-based counterparts — the ability to achieve much higher power per given die size, at much faster switching speeds, and with excellent thermal performance.

Contrary to popular opinion, all of these characteristics actually lead to the employment of fewer power devices, magnetics, and respective gate drivers, actually yielding a lower system cost when compared with Si-based high-power designs (e.g., OBCs, string inverters). From growing the boules to the fabrication and device packaging, the stringent qualification process for SiC devices has been thoroughly developed. Moreover, with over 30 years of legacy in SiC, Wolfspeed power devices have experienced over 6 trillion field hours — reaching a point at which data on long-term reliability can be adequately ascertained.

This article dives into the qualification process of SiC components and how this yields high extrinsic device reliability while looking into the accumulated data on long-term wear-out for SiC. There is an additional discussion regarding industry capacity and continuity of supply to support the ever-growing demand for SiC-based devices.

Why Silicon Carbide?

The SiC power device has steadily infiltrated a number of industry verticals for power devices from solar power conversion, power grid systems, industrial motor conversion, and on-board charging for EVs. The proliferation of SiC-based MOSFETs and diodes are for a good reason — when compared with standard Si-based power devices (e.g., IGBTs, SJ MOSFETs), SiC devices offer half the losses, at a third of the size, and with 20% lower system costs. The higher power conversion per die size is due to the fact that SiC has nearly 3× the bandgap, 10× the breakdown electric field, over 2× the thermal conductivity, and 5× the power density when compared with Si.

As more and more designers are currently, or have in the past, designed with SiC, several fundamental long-term effectiveness questions based on SiC quality, reliability, and supply crop up. Some frequently asked questions include:

- What qualifications do you apply to SiC?

- How do I know if SiC is reliable?

- What capacity will the SiC market need and will it have enough?

- How do you predict long-term wearout with SiC?

These are critical questions for vendors to ask in order to position themselves strongly within the power device market long term. The Si substrate has a familiarity within the industry from its fabrication to packaging and device-level completion — the technology has been able to mature over 60 years in the fab and the field. However, this does not outweigh SiC in the power device market. Wolfspeed has over 30 years of legacy with SiC, from delivering the world’s first SiC MOSFET in 1987 to being the only vertically integrated SiC manufacturer from growing the SiC boules to packaging die — all while steadily driving up voltage and current ratings, increasing wafer diameters to bring down cost per unit, and meeting stringent industry and automotive qualifications. The massive benefit of this focused effort over three decades? The collection of relevant data to perform in-depth reliability analysis comparable with that of Si.

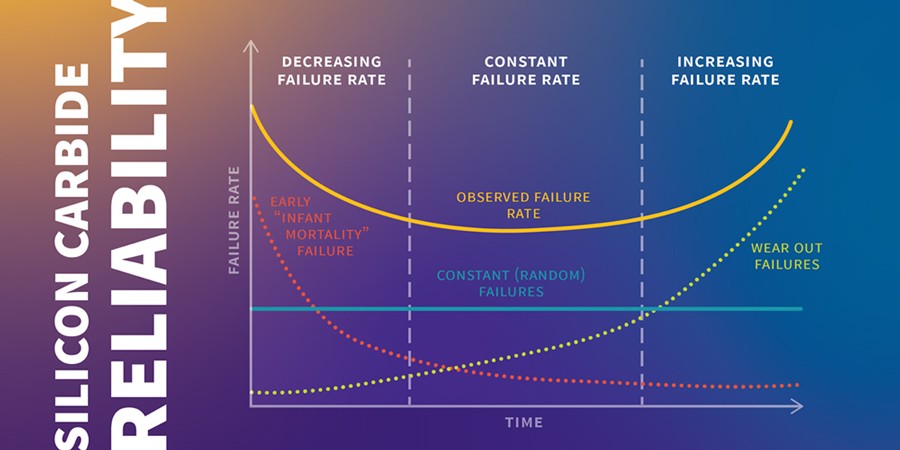

A basic glance at quality and reliability: The bathtub curve

Reliability engineers are familiar with the basic bathtub curve to understand the varying regions of device failures (Figure 1). The first region (Region I) of the bathtub curve includes wear-in failures, or “infant mortality,” and is often dependent on rigorous device qualification. Region II of the bathtub curve relates to the steady state, or field failure rate with constant (random) failures such as external stressors that lead to failures. Finally, Region III of the curve relates to long-term wear-out of the device with accumulation of damage over time. Each of these regions of the bathtub curve correlate to different types of deterioration modeling. In other words, the three areas that the market cares about involve the following:

- Extrinsic failures in the early life of the device

- Observed failures during the steady-state field life of the device

- Intrinsic failures that occur as the device ages

For the power device, the first region relies on qualification testing. The second region relies on device hours (e.g., 1,000 hours, 10,000 hours, 1 million hours) in the field to accumulate sufficient data to acquire a failure in time (FIT) rate. The third region relies on lifetime prediction models and mean time to failure (MTTF) calculations.

Extrinsic reliability: SiC-specific potential failure mechanisms for infant mortality

SiC MOSFETs involve several salient features that, when optimized, offer high quality and more reliability. These include:

- The SiC epitaxial layer (e.g., defects, thickness, doping)

- MOS channel (e.g., inversion-layer mobility, gate dielectric)

- Edge terminations

- Implantation/doping

- Ohmic contacts

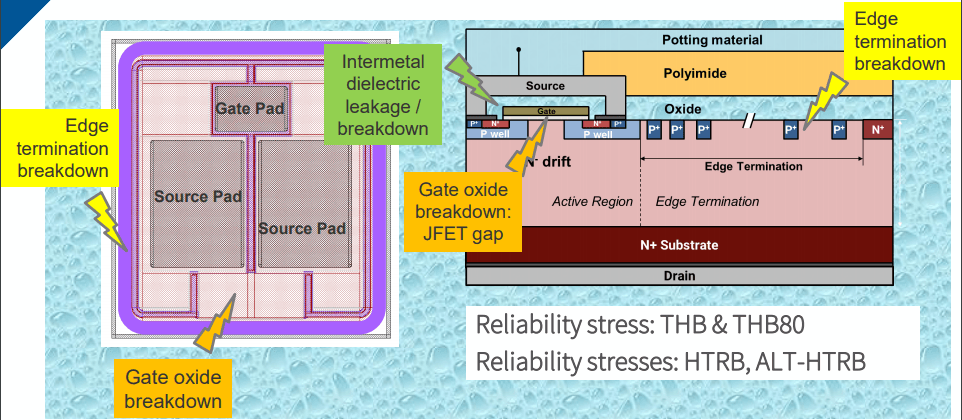

The two potential failure modes of a SiC device are related to blocking voltage and gate voltage. Figure 2 shows the common failure mechanisms in SiC devices as well as some industry reliability tests to ensure proper operation of the MOSFET.

Gate oxide breakdown

Gate oxide breakdown can occur in SiC MOSFETs due to the smaller thickness of the gate oxide layer combined with the application of a higher electric field relative to Si-based devices. This can cause the threshold voltage to increase over long periods of time. However, this problem is sidestepped when MOSFET gate voltage is regularly switched between on and off states as the threshold voltage reverses during the switch.

Edge termination breakdown

In planar structures, breakdown voltages at planar junctions can limit the potential reverse-bias blocking capability of SiC MOSFETs due to an electric field crowding effect. With this effect, the electric field becomes spatially non-uniform and causes crowding at the device periphery. Effective edge termination structures can mitigate this effect and increase device reliability. In most devices, the blocking voltage does not reach the ideal breakdown value for one of two reasons: defects in the active area or the electric field crowding effect. There is, however, a balancing act between edge termination length (termination area) and material cost. It is therefore optimal to strike a balance between the two.

Intermetal dielectric leakage/breakdown

The electrical and thermal performance of the interconnect in power devices become more challenging as device dimensions become smaller. The intermetal dielectric (IMD) breakdown relates to the IMD leakage current that occurs in the event of dielectric breakdown due to a high voltage pulse or continuous power. This is typically tested with the time-dependent dielectric breakdown (TDDB) test in order to screen out defect-related breakdowns that can lead to infant mortality.

Steady-state field reliability: Silicon Carbide-specific potential random failure mechanisms

Neutron collisions

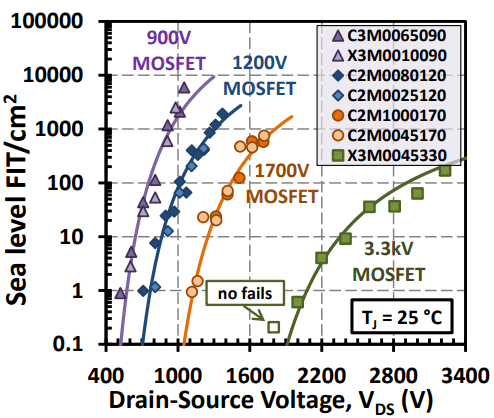

More often than not, the random failure mechanism for an already-qualified SiC device would be due to cosmic radiation. Terrestrial neutron irradiation occurs when neutrons collide with lattice atoms in the power device; this causes atoms to recoil and protons and/or neutrons to be emitted. Charges spike along these trajectories, leaving ionization trails that are not negligible — on the order of micrometers, which is comparable with epilayer thickness. The current transients that are induced by the neutron collision can cause failures in both bipolar and MOSFET-type SiC devices. In the bipolar NPN, bipolar turn-on can occur, causing burnout. In the MOSFET, charge accumulation can occur, causing a gate oxide failure.

The SiC device has an intrinsically higher reliability when compared with Si counterparts (e.g., IGBTs) due to the relatively smaller die size — there is far less physical area to get hit with a neutron bomb. As demonstrated by the graph in Figure 3, the failure rates increase proportionally with device area while the failure rates also decrease as voltage rating increases. This is the main failure mechanism at steady-state, particularly for high-altitude applications such as aerospace, high-altitude power installations, or even an EV driving around a mountain.

The first third of the bathtub curve: How are Silicon Carbide devices qualified?

With these common failure mechanisms in mind, Wolfspeed utilizes proven industry-standard testing to ensure the SiC devices are of the utmost quality prior to releasing them (Figure 2). This includes the qualification testing across large samples sizes in different lots to ensure a 90% confidence, or <1% failure rate. The product qualification that the SiC devices undergo ensures a high extrinsic reliability.

Wolfspeed leverages industrial (JEDEC) and automotive standards (AEC-Q101) that were constructed around silicon. The AEC-Q101 standard is generally more stringent than the JEDEC: The automotive standard requires 77 samples to be tested across three separate lots, while the JEDEC industrial standards require 25 samples across three lots. The AEC standards require the high levels of electrical and optical screening available and also monitor drift and shift within the lots under test. The major industry consortia including JEDEC, IEC, AEC, and JEITA are all actively developing SiC-specific standards to meet the needs for SiC technology and customer base. Wolfspeed is integrally involved in this process, working with subcommittees and task groups on SiC reliability and qualification testing.

Typically, a higher failure rate is seen at the extrinsic part of the bathtub curve, as this is the stage where faulty components are screened out. Table 1 lists the typical product qualification that a SiC device undergoes at Wolfspeed. Table 2 lists how these stress tests relate to performance for devices that require a high drain bias, high altitude, high humidity, high gate bias, or third-quadrant operation — each of these requirements relate to specific potential failure mechanisms. A high blocking voltage requires a high electrical field reliability, while a high gate oxide voltage needs a high gate oxide reliability. A high switching speed necessitates a high threshold voltage (VGS(th)) stability, high body diode is requisite for third-quadrant operation, and finally, there is a need for high terrestrial neutron reliability for high-altitude applications.

Table 1

Typical Product Qualification

Stress Test | Sample Size Per Lot | # of Lots | Reference Standard | Requirements/Description | Accept on # Failed | |

|---|---|---|---|---|---|---|

High Temperature Reverse Bias | HTRB | 77 | 3 | MIL-STD-750-1 M1038 Method A | 1000 hours at Vmax and Tcmax | 0 |

High Temperature Gate Bias | HTGB | 77 each Vgs>0 and Vgs<0 | 3 | JESD22 A-108 | 1000 hours at Vmax and Vgasmin and Tcmax | 0 |

Temperature Cycling | TC | 77 | 3 | JESD22 A-104 | 1000 cycles Ta_max/Ta_min | 0 |

Unbiased Highly Accelerated Stress Test | UHAST | 77 | 3 | JESD22 A-118 | 96 hours at 130C and 85% RH | 0 |

High Humidity High Temperature Reverse Bias | H3TRB | 77 | 3 | JESD22 A-101 | 1000 hours at 85C, 85% RH with device reverse biased to 100V | 0 |

Intermittent Operational Life | IOL | 77 | 3 | MIL-STD-750 M1037 | 6000 cycles, 5 minutes on/5 minutes off, devices powered to ensure DTJ≥100C | 0 |

Destructive Physical Analysis | DPA | 2 | 3 | AEC-Q101-004 Section 4 | Random sample of parts that have successfully completed H3TRB and TC | 0 |

Time-dependent Dielectric Breakdown | TDDB | - | - | - | Apply high gate voltage and test time to failure | - |

Negative Bias Temperature Instability | NBTI | - | - | - | Measure of threshold voltage shift with time | - |

High Temperature Storage | HTS | - | - | - | 1000 hours Tstorage_max | - |

Low Temperature Storage | LTS | - | - | - | 1000 hours Tstorage_min | - |

Vibration | - | - | - | - | Sinusouidal sweep at nominal g (e.g., 5 g), # of hours per x, y, z axis | - |

Mechanical Shock | - | - | - | - | Half sine pulse at high g (e.g., 30g), # of times in the x, y, z direction | - |

Table 2

Potential Failure Mechanisms and Corresponding Standard Tests

Requirement | Gate Oxide Breakdown | SiC Breakdown | Bipolar NPN | Edge Termination Breakdown | Threshold Voltage Drift | Increased resistance and Reduced Current Flow |

|---|---|---|---|---|---|---|

High drain bias | HTRB, ALT-HTRB | HTRB, ALT-HTRB | HTRB, ALT-HTRB | HTRB, ALT-HTRB | ||

High altitude | n-irradiated HTRB | n-irradiated HTRB | n-irradiated HTRB | |||

High humidity | THB | THB | ||||

High gate bias | TDDB, HTGB | NBTI, PBTI | ||||

3rd quadrant | Body diode HTOL |

The middle of the bathtub curve: FIT rates

Observed failures

As stated earlier, Wolfspeed’s legacy in SiC has allowed the compilation of massive amounts of data — over 6 trillion field hours. From this data, FIT rate analysis has been performed on various Wolfspeed SiC devices, as shown in Table 3. While qualification is paramount to ensure basic field reliability, the failures that occur post-qualification truly dictate the viability of the supplier and the quality of the technology. The FIT rates are calculated according to industry standards, wherein the first three months of sale are discounted, the actual field hours are ascertained by factoring in when the device is not being used, and the failures due to cosmetic reasons (e.g., part returns) are discounted from the calculation for accuracy.

As seen in the table, the Wolfspeed FIT rates are typically below 5% ppb and decrease with an increase in field device hours. For this reason, the C6D diode appears to have the highest FIT rate, as it is at the tail end of the extrinsic part of the bathtub curve as a relatively new product.

Table 3

Wolfspeed SiC Power Device Field Reliability

Technology | Fielded Device Hours (billions) | FIT Rate (valid field failures per billion device hours) |

|---|---|---|

C3Dxxx060 Diode | 4893 | 0.05 |

C4Dxxx120 Diode | 839 | 0.2 |

C2M MOSFET | 129 | 3.3 |

C3M MOSFET | 51 | 2.3 |

The last third of the bathtub curve: How do I know if Silicon Carbide is reliable?

Blocking voltage and gate voltage long-term wear-out

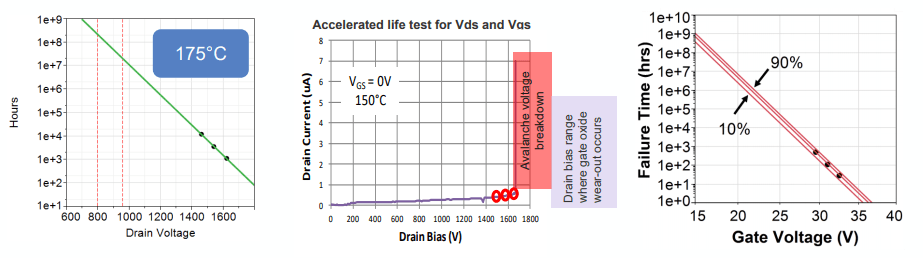

The reliability testing of SiC devices and the various lifetime prediction models reveal the typical failure mechanism as the device ages. Wolfspeed employs common testing techniques for intrinsic wear-out by pushing the device to way over the maximum voltage rating or current rating for as long as possible and under the worst conditions possible. In Figure 4, a 1,200-V–rated Wolfspeed MOSFET is pushed up to 1,700 V and predicted hours of operation are obtained based upon this stress.

It should be noted that a 1,200-V–rated Si device generally rolls out at about 1,250 V; therefore, SiC devices generally have much more margin on their voltage ratings. Typically, a 1,200-V–rated SiC MOSFET is working on a 700- to 800-V bus — in this case, there are over 300 million hours of theoretical safe operation before the device fails from a failure mechanism due to blocking voltage. The very same process is applied to gate voltage with the TDDB method.

The TDDB method is another method of understanding the MTTF of power devices. This method subjects a population of MOSFETs to a constant bias at accelerated bias conditions as well as elevated temperatures. The failure time statistics are calculated and Weibull distributions are fit to the failure statistics to estimate lifetime. In Figure 4, a device with a gate voltage rating of 15 V is pushed to beyond 35 V and the probability of failure at the rated gate voltage becomes 50 million device hours. For the Gen3 650-V Wolfspeed MOSFETs, the MTTF stands at 70 million hours at 15-V continuous gate bias, showing a nearly identical gate reliability to the 1,200-V and 1,700-V MOSFETs.

Wolfspeed’s reliability bathtub curve calculator

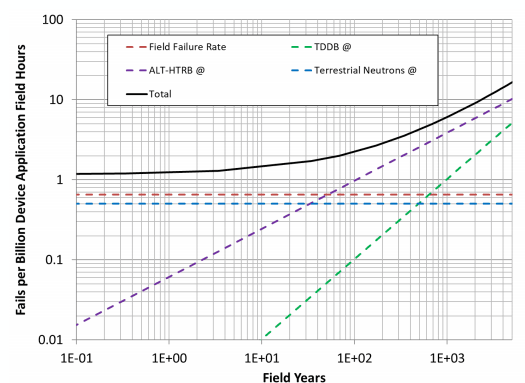

In order to accurately assess all regions of the bathtub curve for their SiC devices, Wolfspeed developed a bathtub curve calculator that uses a mission profile as input. As shown in Figure 5, this profile is based upon field, qualification, and testing parameters such as VG, VD, TJ, altitude, and an hours histogram.

Power and packaging reliability

While much work is done to ensure the successful operation of a bare die SiC, the power and packaging is an unavoidable reliability issue for both Si and SiC alike. Typically, power packaging is the weakest link, especially at higher temperatures where the failures tend to be more intrinsic in nature (e.g., wire bonds and die attach rip off) The industrial power cycling test is the standard way to characterize the wire bond thermomechanical fatigue wear-out mechanism. It has been shown that the reliability performance is comparable between SiC and Si devices and that failures occur due to thermomechanical fatigue for both types of devices regardless of substrate material.

Understanding Silicon Carbide production capacity

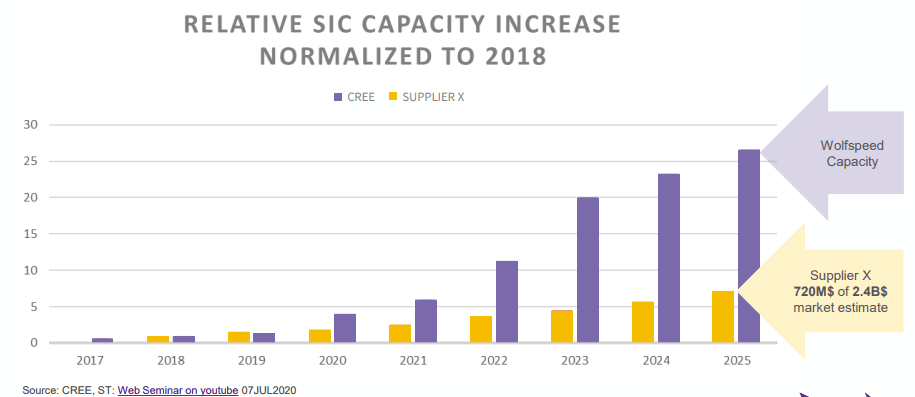

Now that it is well established that SiC is both high-quality and high-reliability, with sufficient data to prove so, the question then pivots to the ability to supply these devices. Wolfspeed is fully invested in meeting present and future demand with a billion-dollar investment in the largest state-of-the-art dedicated SiC fabrication facility. This allows for 30× the original capacity of Wolfspeed, meeting the predicted world market growth of a tenfold increase in SiC semiconductors from 2018 to 2024. This is a considerable growth in capacity when compared with other market suppliers of this semiconductor, wherein the closest supplier comes in to serve approximately $720 million of the $2.4 billion market estimate — meeting only a fraction of the capacity capability that Wolfspeed has (Figure 6).

Conclusion

SiC semiconductor applications are expanding greatly due to their excellent performance, power capacity, efficiency, die size, and relative cost-effectiveness. With over 30 years to compile past and present data, there is a large swath of information that allows for FIT rate analysis and extrinsic characterization, ensuring that SiC products are of high quality. This momentum is pushing standards committees to develop and evolve SiC-specific industrial standards, allowing for the continued maturity and utilization of SiC technology. Long-term wear-out and reliability analysis is continually being performed to better assess the failure mechanisms of these devices due to aging, and while it is not as established as Si devices that have had over 60 years of legacy, this data is maturing for more accuracy and dependability.

Wolfspeed is a leading vendor in SiC technology as the only vertically integrated SiC manufacturer with a significant investment in ensuring any and all SiC devices are robust prior to launch. This has also allowed for the continual progression of a strong support ecosystem with design software and tools to implement SiC.

With 6 trillion field hours of data to build upon, extended wear-out studies, and FIT rates in the single digits, Wolfspeed is leading the way on quality, long-term reliability, and safe use of SiC devices.