Selecting Between Wolfspeed’s Design Tools

Article

The design of a power electronics system is a complex engineering problem. Traditionally, overcoming its challenges required time consuming analytical analysis performed by subject matter experts. Fortunately, engineers have a variety of modern tools that can significantly expedite the design process and optimize results. These tools range from software simulation tools, such as PLECS® and SPICE, to measurement-based methods, such as dynamic performance characterization. Each analysis approach has its own advantages and limitations that make them suitable to answer specific design questions, which will be described here.

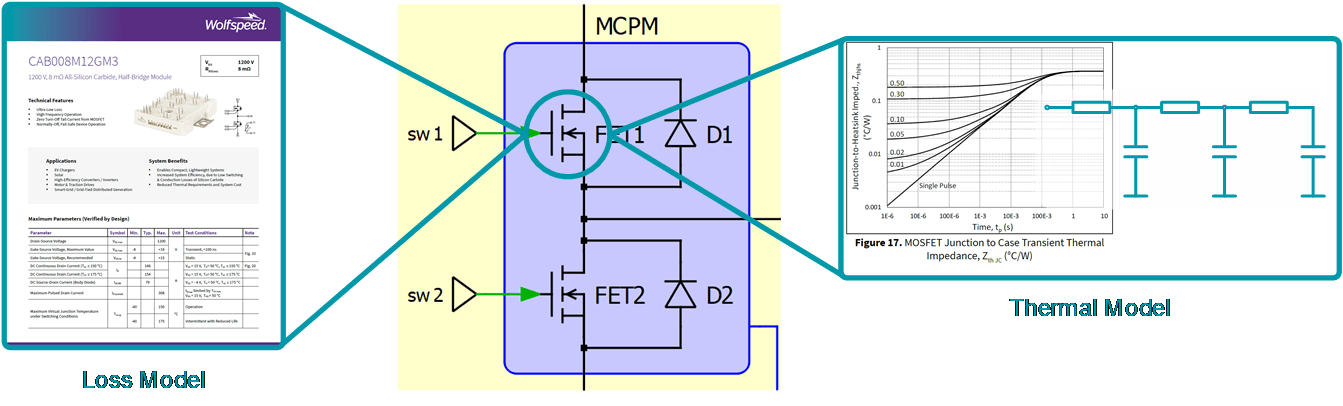

PLECS® is a simulation tool developed specifically for power electronics system simulation and can aid engineers in the design of control schemes, topologies, and thermal systems. It offers multiple physics domains to simplify analysis of mechanical, thermal, or magnetic components of the system. PLECS® uses an ideal switch model for transistors and dynamically selects integration timesteps before and after an instantaneous change in transistor resistance. For switching circuit applications, this analysis approach gives a large speed advantage to PLECS® over traditional circuit-level simulations. Because electrical components are idealized, power losses are analytically described (by lookup table or function) to match experimental results. Wolfspeed’s PLECS models are built from the datasheet information, as shown in Figure 1. In general, PLECS® is extremely useful for control design, device selection, predicting system losses, predicting device junction temperature, and thermal system design. In addition to offering a complete portfolio of PLECS® models for download, Wolfspeed freely offers SpeedFit, an online evaluation tool for system design questions.

While PLECS® is a powerful simulation tool, it is not without limitations. For example, transistor models in PLECS® are developed using datasheet data, so the switching energy considered is the typical value for a low inductance system. Similarly, the conduction losses and thermal model use typical datasheet values. Therefore, it is always critical to leave design margin as corner case devices will have higher junction temperatures than the nominal TJ predicted by PLECS® (due to higher losses and higher thermal impedance). Generally, design of the maximum per cycle temperature delta should be designed using lifetime models, as allowing swings between TFLUID and TJ,MAX may not guarantee the desired system operational lifetime. Additionally, the electrical signals in the system model should be considered with caution. While low frequency behavior (such as ripple voltage, output current, and power factor) is accurately simulated, dynamics which result from the device switching cannot be predicted in PLECS®. Therefore, parameters such as device edge rates and voltage overshoot are not captured by the simulation, and there is no purpose to modeling parasitics elements, since their contribution is not relevant in the simplified electrical simulation.

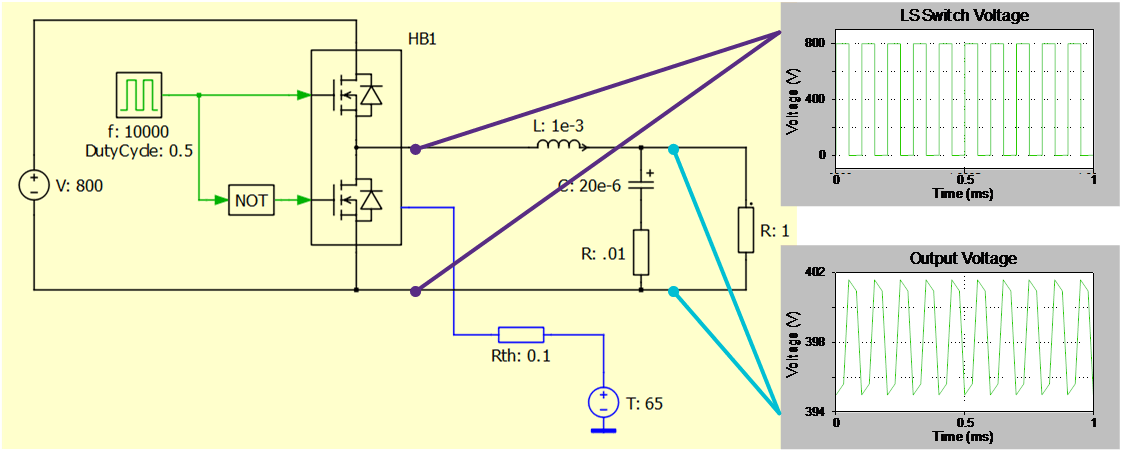

In order to demonstrate both the idealized switching and low frequency circuit dynamics, Figure 2 shows a buck converter simulation in PLECS. The low-side switch voltage demonstrates that hard switching behavior is simplified to a simple square wave; slew rates, overshoot, rise / fall time, and other dynamic characteristics are not simulated. However, as seen by the output voltage waveform, the electrical domain waveforms can still be useful as many parameters such as output ripple can still be simulated without precise switching dynamics. In general, low frequency phenomena determined by the power electronics and filter passives will be correctly simulated in PLECS.

Unlike PLECS®, circuit-level simulators (such as SPICE) attempt to predict the detailed switching transient events, which allows them to simulate many electrical dynamics ignored in PLECS®. Circuit-level simulations should be the tool of choice for studies which require device transients. Some possible examples include dynamic current sharing, Monte Carlo analysis, or electromagnetic compatibility (EMC) analysis. Unfortunately, the increase in model complexity also comes with a significant penalty to simulation speed. For converter simulations, thousands of these dynamic events must be computed per second simulated, making these models slow and impractical for control or thermal design. Additionally, while the transient events are simulated, precise prediction of the switching event should not be assumed as it requires an accurate model of the transistor, circuit parasitics, and gate drive. Therefore, using the Wolfspeed provided SPICE models for “dynamic evaluation” is not advised.

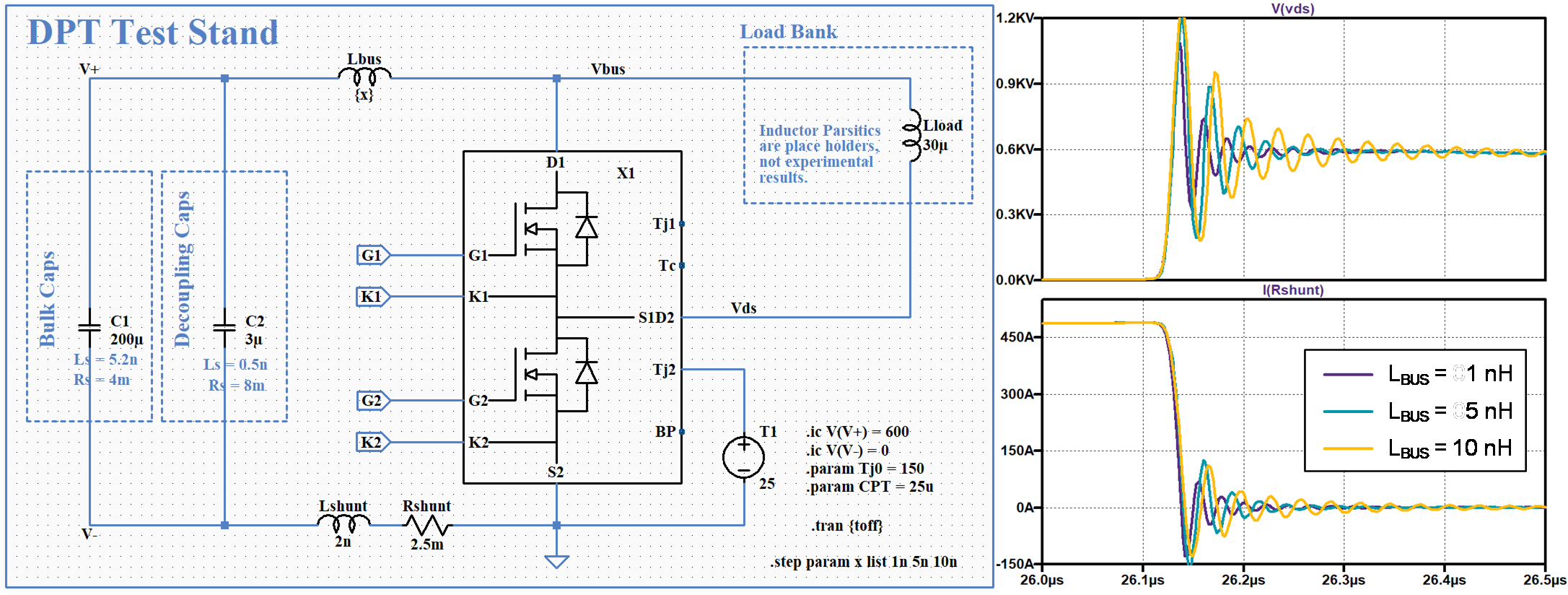

As a practical example, Figure 3 shows an example SPICE simulation of a clamped inductive load circuit (similar to Wolfspeed’s evaluation kits). Sweeping the bus inductance causes a large change in overshoot voltage, ringing frequency, and damping ratio. Specifically, a change in bus inductance of 9 nH leads to an overshoot prediction difference of 200 V. Similar effects can be created by changes to the gate drive model and even larger discrepancies from changes to the transistor model. Therefore, using SPICE models to predict detailed device dynamics can range from challenging to misleading.

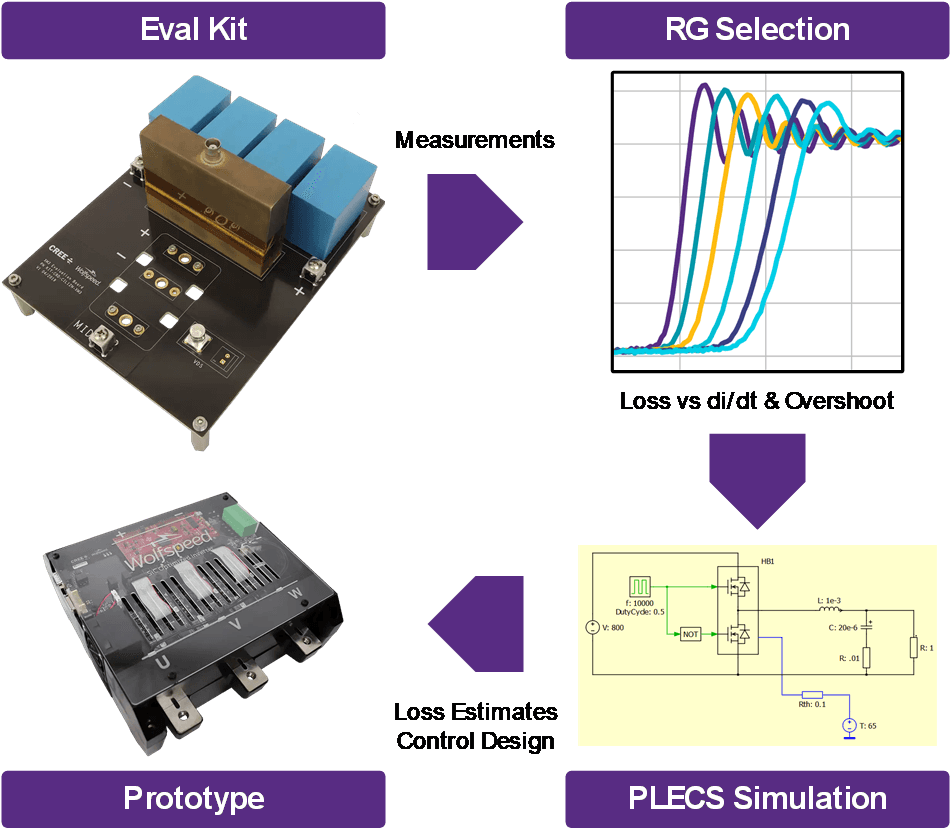

If dynamic characteristics beyond the information provided in the datasheet is required, consider using measurement instead of SPICE. While getting accurate device measurements can be an expensive and involved process, Wolfspeed offers dynamic performance evaluation kits for all its products, some of which can be borrowed through the Arrow Testdrive program. These dynamic characterization evaluation kits simplify the measurement process as they feature low parasitic inductance and high-quality metrology (which is often a major hurtle to measuring switching signals during the prototyping phase). They are ideal for measuring timing (TDelay-On, TDelay-Off, TRise, TFall), overshoot (VDS-Max, ID-Max), switching speed (di/dt, dv/dt), and switching energy (EON, EOFF, ERR), but these measurements will require a high bandwidth oscilloscope and probes (at least 100’s of MHz). Characterization of the high-side gate or drain voltage will also require differential probes with high voltage isolation. Finally, the evaluation kits include a current viewing resistor (CVR) which can be utilized for measuring device current. To highlight the capabilities of the evaluation kit, Figure 4 demonstrates a sweep of gate resistance which was conducted on a Wolfspeed CIL evaluation kit.

All three methods have applications in the power electronics design process, and each should be leveraged during the design process as appropriate.

PLECS® | Circuit-Level | Measurement | |

|---|---|---|---|

Example Applications | System Evaluation Device Selection Control Design Thermal Design | Dynamic Current Sharing Monte Carlo Simulations EMC Analysis | Dynamic Measurements Overshoot (RBSOA) Gate Resistor Selection Short Circuit Analysis |

Pro | Focused tool, helpful features | General tool, unlimited possibilities | Correct choice for dynamic evaluation |

Con | Simplifies switching events in electrical domain | Model prediction influenced by circuit (e.g. Gate Drive model, parasitics, etc.) | Requires equipment Proper metrology is non-trivial (evaluation kit recommended) |

Simulation Speed | On the order of seconds simulated per second | On the order of milliseconds simulated per second | NA |

Free Options | LTspice® | Eval kits available on loan through Arrow Testdrive program | |

Paid Options | PLECS® Standalone PLECS® Blockset | Ex. OrCAD® PSpice®, PathWave ADS | Available for Purchase |

To learn more about our design tools, view our tools and support landing page or ask an expert in the Wolfspeed power applications forum.